# M.E. VLSI DESIGN

· s . s . . . .

### **VLSI DESIGN**

### VISION OF THE INSTITUTION

To emerge as a centre of excellence and eminence by imparting futuristic technical education in keeping with global standards, making our students technologically competent and ethically strong so that they can readily contribute to the rapid advancement of society and mankind.

### MISSION OF THE INSTITUTION

- To achieve Academic excellence through innovative teaching and learning practices.

- To enhance employability and entrepreneurship.

- To improve the research competence to address societal needs.

- To inculcate a culture that supports and reinforces ethical, professional behaviours for a harmonious and prosperous society.

### VISION OF THE DEPARTMENT

The vision of ECE department is to become pioneer in higher learning and research and to produce creative solution to societal needs.

### MISSION OF THE DEPARTMENT

- 1. To provide excellence in education, research and public service.

- 2. To provide quality education and to make the students entrepreneur and employable.

- 3. Continuous upgradation of techniques for reaching heights of excellence in a global perspectives.

### **PROGRAM OUTCOMES**

### Ability to

- 1. Acquire in-depth knowledge in the field of VLSI Design with an ability to evaluate and analyse the existing knowledge for enhancement

- 2. Analyse critical complex engineering problems and provide solutions through research

- 3. Identity the areas for the development of Electronic hardware design for the benefit of the society

- 4. Extract information pertinent to challenging problems through literature survey and by applying appropriate research methodologies, techniques and tools to the development of technological knowledge

- 5. Select, learn and apply appropriate techniques, resources and modern engineering tools to complex engineering activities with an understanding of limitations

- 6. Understand group dynamics, recognise opportunities and contribute positively to multidisciplinary work to achieve common goals for further learning

- 7. Demonstrate engineering principles and apply the same to manage projects efficiently as a team after considering economical and financial factors

- 8. Communicate with engineering community and society regarding complex engineering activities effectively through reports, design documentation and presentations

- 9. Engage with commitment in life-long learning independently to improve knowledge and competence

- 10. Acquire professional and intellectual integrity, professional code and conduct, ethics of research and scholarship by considering the research outcomes to the community for sustainable development of society

- 11. Observe and examine critically the outcomes and make corrective measures, and learn from mistakes without depending on external feedback

### PROGRAM EDUCATIONAL OBJECTIVES:

- 1. Acquire indepth knowledge, analyse and solve complex problems through research in the field of electronics after considering public health, safety, cultural and societal needs

- 2. Apply the acquired research skills using modern tools and techniques to solve the challenging problems in multidisciplinary areas

- 3. Apply the learnt engineering principles for project and finance management and communicate with society effectively

- 4. Acquire professional and intellectual integrity, ethics of research for sustainable development of society through independent and lifelong learning

# CHOICE BASED CREDIT SYSTEM CURRICULUM FOR CANDIDATES ADMITTED DURING 2016 ONWARDS BRANCH: M.E. (VLSI DESIGN)-FULL TIME

M.E. VLSI DESIGN

### 2016 REGULATIONS

### FIRST SEMESTER

| Sl. | Course   |                                |          | Continuous          | End          | Total |     | Cre | dits |     |

|-----|----------|--------------------------------|----------|---------------------|--------------|-------|-----|-----|------|-----|

| No. | Code     | Course Title                   | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L   | Т   | P    | С   |

|     |          | THEORY                         |          |                     |              |       |     |     |      |     |

| 1   | 16VLFC01 | Applied Mathematics            | FC       | 50                  | 50           | 100   | 3   | 2   | 0    | 4   |

| 2   | 16VLPC01 | Advanced Digital System Design | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3 - |

| 3   | 16VLPC02 | Digital CMOS VLSI Design       | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3,  |

| 4   | 16VLPC03 | VLSI Design automation         | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3 , |

| 5   |          | Professional Elective – I      | PE       | 50                  | 50           | 100   | 3   | 0   | 0    | 3,  |

|     |          | PRACTICAL                      |          |                     |              |       |     |     |      |     |

| 6   | 16VLPC04 | VLSI Design Laboratory         | PC       | 50                  | 50           | 100   | 0   | 0   | 4    | 24  |

|     |          | TOTAL                          |          | 300                 | 300          | 600   | 15/ | 2,  | 4,   | 18, |

### SECOND SEMESTER

| Sl. | Course   |                                |          | Continuous          | End          | Total |     | Cre | dits |     |

|-----|----------|--------------------------------|----------|---------------------|--------------|-------|-----|-----|------|-----|

| No. | Code     | Course Title                   | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L   | Т   | P    | С   |

|     |          | THEORY                         |          |                     |              |       |     |     |      |     |

| 1   | 16VLPC05 | Analog VLSI                    | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3   |

| 2   | 16VLPC06 | Low Power VLSI Design          | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3 - |

| 3   | 16VLPC07 | VLSI-Signal Processing         | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3 - |

| 4   | 16VLPC08 | ASIÇ Design                    | PC       | 50                  | 50           | 100   | 3   | 0   | 0    | 3   |

| 5   |          | Professional Elective - Il     | PE       | 50                  | 50           | 100   | 3   | 0   | 0    | 3   |

| 6   |          | Professional Elective - III    | PE       | 50                  | 50           | 100   | 3   | 0   | 0    | 3   |

|     |          | PRACTICAL                      |          |                     |              |       |     |     |      |     |

| 7   | 16VLPC09 | System Level Design Laboratory | PC       | 50                  | 50           | 100   | 0   | 0   | 4    | 2   |

|     |          | TOTAL                          |          | 350                 | 350          | 700   | 18′ | 0,  | 4.   | 20, |

### THIRD SEMESTER

| SI. | Course   |                            |          | Continuous          | End          | Total |    | Cı | redits |     |

|-----|----------|----------------------------|----------|---------------------|--------------|-------|----|----|--------|-----|

| No. | Code     | Course Title               | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L  | Т  | P      | С   |

|     |          | THEORY                     |          |                     |              |       |    |    |        |     |

| 1   |          | Professional Elective - IV | PE       | 50                  | 50           | 100   | 3  | 0  | 0      | 3.  |

| 2   |          | Professional Elective - V  | PE       | 50                  | 50           | 100   | 3  | 0  | 0      | 3 ″ |

| 3   |          | Professional Elective - VI | PE       | 50                  | 50           | 100   | 3  | 0  | 0      | 3.  |

|     |          | PRACTICAL                  |          |                     |              |       |    |    |        |     |

| 4   | 16VLEE01 | Project Phase I            | EEC      | 100                 | 100          | 200   | 0  | 0  | 12     | 6.  |

|     |          | TOTAL                      |          | 250                 | 250          | 500   | 9, | 0. | 12,    | 15, |

### FOURTH SEMESTER

| Sl. | Course<br>Code | Course Title     |          | Continuous<br>Assessment<br>Marks | End          | Total |   | С |    |    |

|-----|----------------|------------------|----------|-----------------------------------|--------------|-------|---|---|----|----|

| No. |                |                  | Category |                                   | Sem<br>Marks | Marks | L | Т | P  | C  |

|     |                | PRACTICAL        |          |                                   |              |       |   |   |    |    |

| 1   | 16VLEE02       | Project Phase II | EEC      | 200                               | 200          | 400   | 0 | 0 | 24 | 12 |

|     |                | TOTAL            |          | 200                               | 200          | 400   | 0 | 0 | 24 | 12 |

# CURRICULUM FOR CANDIDATES ADMITTED DURING 2016 ONWARDS BRANCH: M.E.(VLSI DESIGN)-PART TIME

M.E. VLSI DESIGN

### 2016 REGULATION

### FIRST SEMESTER

| SI. | Course   |                                |          | Continuous          | End          | Total |     | Credits |   |     |  |

|-----|----------|--------------------------------|----------|---------------------|--------------|-------|-----|---------|---|-----|--|

| No. | Code     | Course Title                   | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L   | Т       | P | С   |  |

|     |          | THEORY                         |          |                     |              |       |     |         |   |     |  |

| 1   | 16VLFC01 | Applied Mathematics            | FC       | 50                  | 50           | 100   | 3   | 2       | 0 | 4 * |  |

| 2   | 16VLPC01 | Advanced Digital System Design | PC       | 50                  | 50           | 100   | 3   | 2       | 0 | 4 - |  |

| 3   | 16VLPC02 | Digital CMOS VLSI Design       | PC       | 50                  | 50           | 100   | 3   | 0       | 0 | 3=  |  |

|     |          | TOTAL                          |          | 150                 | 150          | 300   | 9 , | 4       | 0 | 11  |  |

### SECOND SEMESTER

| Sl. | Course   | Course Code Course Title Category |                     | Continuous   | End   | Total | Credits |   |   |    |  |

|-----|----------|-----------------------------------|---------------------|--------------|-------|-------|---------|---|---|----|--|

| No. |          |                                   | Assessment<br>Marks | Sem<br>Marks | Marks | L     | Т       | P | С |    |  |

|     |          | THEORY                            |                     |              |       |       |         |   |   |    |  |

| 1   | 16VLPC05 | Analog VLSI                       | PC                  | 50           | 50    | 100   | 3       | 0 | 0 | 3  |  |

| 2   | 16VLPC06 | Low Power VLSI                    | PC                  | 50           | 50    | 100   | 3       | 0 | 0 | 3  |  |

| 3   | 16VLPC07 | VLSI Signal Processing            | PC                  | 50           | 50    | 100   | 3       | 0 | 0 | 3  |  |

|     |          | TOTAL                             |                     | 150          | 150   | 300   | 9,      | 0 | 0 | 9. |  |

### THIRD SEMESTER

| SI. | Course   |                           |          | Continuous          | End          | Total | Credits |   |     |     |  |  |

|-----|----------|---------------------------|----------|---------------------|--------------|-------|---------|---|-----|-----|--|--|

| No. | Code     | Course Title              | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L       | Т | P   | С   |  |  |

|     |          | THEORY                    |          |                     |              |       |         |   |     |     |  |  |

| 1   | 16VLPC03 | VLSI Design automation    | PC       | 50                  | 50           | 100   | 3       | 0 | 0   | 3 1 |  |  |

| 2   |          | Professional Elective - I | PE       | 50                  | 50           | 100   | 3       | 0 | 0   | 3.  |  |  |

|     |          | PRACTICAL                 |          |                     |              |       |         |   |     |     |  |  |

| 3   | 16VLPC04 | VLSI Design Laboratory    | PC       | 50                  | 50           | 100   | 0       | 0 | 4   | 2 - |  |  |

|     |          | TOTAL                     |          | 150                 | 150          | 300   | 6       | 0 | 4 - | 8,  |  |  |

### FOURTH SEMESTER

| SI. | Course   |                                   |          | Continuous          | End          | Total |   | Cı | redits |      |

|-----|----------|-----------------------------------|----------|---------------------|--------------|-------|---|----|--------|------|

| No. | Code     | Course Title                      | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L | Т  | P      | С    |

|     |          | THEORY                            |          |                     |              |       |   |    |        |      |

| 1   | 16VLPC08 | ASIC Design                       | PC       | 50                  | 50           | 100   | 3 | 0  | 0      | 3    |

| 2   |          | Professional Elective - II        | PE       | 50                  | 50           | 100   | 3 | 0  | 0      | 3    |

| 3   |          | Professional Elective - III       | PE       | 50                  | 50           | 100   | 3 | 0  | 0      | 3    |

|     |          | PRACTICAL                         |          |                     |              |       |   |    |        |      |

| 4   | 16VLPC09 | System Level Design<br>Laboratory | PC       | 50                  | 50           | 100   | 0 | 0  | 4      | 2    |

|     |          | TOTAL                             |          | 200                 | 200          | 400   | 9 | 0  | 4 /    | 11 ' |

### FIFTH SEMESTER

| CI         | Course         |                            |          | Continuous          | End          | Total |   | С | redits |     |

|------------|----------------|----------------------------|----------|---------------------|--------------|-------|---|---|--------|-----|

| SI.<br>No. | Course<br>Code | Course Title               | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L | Т | Р      | С   |

|            |                | THEORY                     |          |                     |              |       |   |   |        |     |

| 1          |                | Professional Elective - IV | PE       | 50                  | 50           | 100   | 3 | 0 | 0      | 3   |

| 2          |                | Professional Elective - V  | PE       | 50                  | 50           | 100   | 3 | 0 | 0      | 3 • |

| 3          |                | Professional Elective - VI | PE       | 50                  | 50           | 100   | 3 | 0 | 0      | 3 🖟 |

|            |                | PRACTICAL                  |          |                     |              |       |   |   |        |     |

| 4          | 16VLEE01       | Project Phase I            | EEC      | 100                 | 100          | 200   | 0 | 0 | 12     | 6 4 |

|            |                | TOTAL                      |          | 250                 | 250          | 500   | 9 | 0 | 12 4   | 15  |

### SIXTH SEMESTER

| CI         | Carrea         |                  |          | Continuous          | End          | Total |   | С | redits |     |

|------------|----------------|------------------|----------|---------------------|--------------|-------|---|---|--------|-----|

| Sl.<br>No. | Course<br>Code | Course Title     | Category | Assessment<br>Marks | Sem<br>Marks | Marks | L | Т | Р      | С   |

|            |                | PRACTICAL        |          |                     |              |       |   |   |        |     |

| 1          | 16VLEE02       | Project Phase II | EEC      | 200                 | 200          | 400   | 0 | 0 | 24     | 12. |

|            |                | TOTAL            |          | 200                 | 200          | 400   | 0 | 0 | 24-    | 12, |

### LIST OF PROFESSIONAL ELECTIVES

| Sl. | Course   | Course Title                                       | Catagomi | Continuous          | End Sem |   | Cre | dits |   |

|-----|----------|----------------------------------------------------|----------|---------------------|---------|---|-----|------|---|

| No. | Code     | Course Title                                       | Category | Assessment<br>Marks | Marks   | L | Т   | P    | С |

| 1   | 16VLPE01 | Image and Video Processing                         | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 2   | 16VLPE02 | Mixed Signal Circuits and<br>Interfacing           | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 3   | 16VLPE03 | RF system Design                                   | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 4   | 16VLPE04 | Microsensors and MEMS                              | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 5   | 16VLPE05 | Graph Theory and Optimization Techniques           | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 6   | 16VLPE06 | Neural Networks                                    | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 7   | 16VLPE07 | Electronic Packaging<br>Technologies               | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 8   | 16VLPE08 | Nano electronics                                   | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 9   | 16VLPE09 | Real Time Operating System                         | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 10  | 16VLPE10 | Embedded controllers                               | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 11  | 16VLPE11 | High performance computer networks                 | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 12  | 16VLPE12 | Analysis and Design of Analog Integrated Circuits. | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 13  | 16VLPE13 | DSP Integrated Circuits                            | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 14  | 16VLPE14 | Hardware software co-design                        | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 15  | 16VLPE15 | Design of semiconductor memories                   | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 16  | 16VLPE16 | System on chip                                     | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 17  | 16VLPE17 | Reconfigurable architecture for VLSI               | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 18  | 16VLPE18 | VLSI interconnects and its design techniques       | 50       | 50                  | 100     | 3 | 0 = | 0    | 3 |

| 19  | 16VLPE19 | VLSI for wireless communication                    | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

| 20  | 16VLPE20 | Testing and testability                            | 50       | 50                  | 100     | 3 | 0   | 0    | 3 |

### LIST OF ONE CREDIT COURSE

| Sl. | Course   | 1                             |          | Continuous          | End Sem |   | Cre | dits |   |

|-----|----------|-------------------------------|----------|---------------------|---------|---|-----|------|---|

| No. | Code     | Course Title                  | Category | Assessment<br>Marks | Marks   | L | Т   | Р    | С |

| 1   | 16VLOC01 | Seminar and Technical Writing | 50       | 50                  | 100     | 0 | 0   | 2    | 1 |

### CREDIT SUMMARY- VLSI DESIGN -FULL TIME

| S.No.  | Subject |    | Credits pe | r Semester |     | Credits | % of<br>Total | Total No. of |

|--------|---------|----|------------|------------|-----|---------|---------------|--------------|

| 5.110. | Area    | I  | II         | III        | IV  | Total   | Credits       | Courses      |

| 1      | FC      | 4  | E .        | 7          | (€  | 4       | 6             | 1            |

| 2      | PC      | 11 | 14         | a.         | 100 | 25      | 39            | 9            |

| 3      | PE      | 3  | 6          | 9          | -   | 18      | 28            | 6            |

| 4      | EEC     | æ  | -          | 6          | 12  | 18      | 28            | 2            |

|        | TOTAL   | 18 | 20         | 15         | 12  | 65      |               |              |

FC – Foundation Course

PC-Professional Core

PE-Professional Elective

EEC-Employment Enhancement Course

### CREDIT SUMMARY- VLSI DESIGN -PART TIME

|       | Subject |    | С   | redits per | Semeste | er |     | Credits | % of             | Total No.  |

|-------|---------|----|-----|------------|---------|----|-----|---------|------------------|------------|

| S.No. | Area    | I  | II  | III        | IV      | V  | VI  | Total   | Total<br>Credits | of Courses |

| 1     | FC      | 4  | = 1 |            | 858     | =  | 3.  | 4       | 6                | 1          |

| 2     | PC      | 6  | 9   | 5          | 5       | *  | 340 | 25      | 39               | 9          |

| 3     | PE      | 3  |     | 3          | 6       | 9  | 727 | 18      | 28               | 6          |

| 4     | EEC     | *  | +   | -          | -       | 6  | 12  | 18      | 28               | 2          |

|       | TOTAL   | 10 | 9   | 8          | 11      | 15 | 12  | 65      |                  |            |

FC - Foundation Course

PC-Professional Core

Centreller of Examinations

Government College of Technology

COIMBATORE - 641 813

PE-Professional Elective

EEC-Employment Enhancement Course

# DEPARTMENT OF ECE VLSI DESIGN L T P C 16VLFC01 APPLIED MATHEMATICS 3 2 0 4

### CORE/ELECTIVE COURSE:Core

### **PREREQUISITES:**

• Basics of algebra, differential and integral formulae.

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

(Common to Applied Electronics)

### **COURSE OBJECTIVES:**

- To acquire knowledge of solving problems on matrix theory, discrete and continuous distributions.

- To develop an understanding of discrete and continuous random processes.

- To acquire knowledge of linear programming problems.

- To familiarize with queuing models.

### **COURSE OUTCOMES:**

Upon completion of this course, the students will have an ability to:

- CO1:Gain the skill of finding eigen values using QR algorithm and the knowledge of discrete and continuous distributions along with functions of random variables.

- CO2:Develop discrete and continuous random processes including Markov processes and also solutions of Linear Programming problems.

- CO3:Understand probability values for various queuing models in situations of single or many service terminals available.

### **TOPICS COVERED:**

LINEAR ALGEBRA (9+6)

Vector spaces – norms – Inner Products – Eigenvalues using QR transformations – QR factorization - generalized eigenvectors– singular value decomposition and applications - pseudo inverse – least square approximations –Toeplitz matrices and some applications.

### ONE DIMENSIONAL RANDOM VARIABLES

(9+6)

Random variables - Probability function - moments - moment generating functions and their properties - Binomial, Poisson, Geometric, Uniform, Exponential, Gamma and Normal distributions - Function of a Random Variable.

### RANDOM PROCESSES (9+6)

Classification – Auto correlation - Cross correlation - Stationary random process – Markov process — Markov chain - Poisson process – Gaussian process.

### LINEAR PROGRAMMING

(9+6)

Formulation – Graphical solution – Simplex method – Two phase method - Transportation and Assignment Models.

QUEUEING MODELS (9+6)

Characteristic and representation of queuing models- Model I:[(M/M/1): ("/FIFO)], Model II [(M/M/S):("/FIFO)], Model III:[(M/M/1): (N/FIFO)], Model IV: [(M/M/S):(N/FIFO)].

### LECTURE: 45 PERIODS TUTORIAL: 30 PERIODS PRACTICAL: 0 PERIODS TOTAL: 75 PERIODS

### Reference Books:

- 1. Bronson, R. Matrix Operation, Schaum's outline series, McGraw Hill, New york (1989).

- 2. Oliver C. Ibe, "Fundamentals of Applied Probability and Random Processes, Academic Press, (An imprint of Elsevier), 2010.

- 3. Taha H.A. "Operations Research: An introduction" Ninth Edition, Pearson Education, Asia, New Delhi 2012.

- 4.Sankara Rao, K. "Introduction to partial differential equations" Prentice Hall of India, pvt, Ltd, New Delhi, 1997.

- 5. Andrews, L.C. and Philips. R. L. "Mathematical Techniques for engineering and scientists", Printice Hall of India, 2006.

- 6. O'Neil P.V. "Advanced Engineering Mathematics", (Thomson Asia pvt ltd, Singapore) 2007, cengage learning India private limited..

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 1   | =   | a   | 1   | 2   | -   | 1-  | *   | 1   | ) := | -    |

| CO2 | -   | 3   |     | 1   | a   | =   | -   | -   | 1   | 1    | 3.   |

| CO3 | 1   | -   | =   | 1   | 2   | 2   | *   | ii. | 1   | ¥1.  | 540  |

| I:  |  |  |  |

|-----|--|--|--|

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

| int |  |  |  |

|     |  |  |  |

|     |  |  |  |

| ıll |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|                                         | L | T | P | C | l |

|-----------------------------------------|---|---|---|---|---|

| 16VLPC01 ADVANCED DIGITAL SYSTEM DESIGN | 3 | 0 | 0 | 3 | ľ |

| (Common to Applied Electronics)         |   |   |   |   |   |

### CORE/ELECTIVE COURSE: Core

### **PREREQUISITES:**

• Digital Electronics, Programmable devices.

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To get knowledge on Verilog HDL programming and ability to design digital syste

- To design and analyze the clocked synchronous and asynchronous sequential Circu

- To get knowledge on Fault diagnosis and Testability algorithms.

### **COURSE OUTCOMES:**

### Upon completion of the course, the students will have:

CO1:Knowledge on Verilog HDL programming and ability to design digital system CO2: Ability to design and analyze the clocked synchronous and asynchronous seq

CO3:Knowledge on Fault diagnosis and Testability algorithms.

### TOPICS COVERED:

### SYSTEM DESIGN USING VERILOG HDL

(9)

Hardware Modeling with Verilog HDL - Logic System, Data Types and Operators for M Verilog HDL - Behavioral Descriptions in Verilog HDL - HDL Based Synthesis - Synthesis State Machines – Structural modeling – Compilation and Simulation of Verilog code –1 Realization of combinational and sequential circuits using Verilog HDL.

### SYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN

(9)

Analysis of clocked synchronous sequential circuits and modeling - State diagram, state assignment and reduction - Design of synchronous sequential circuits - Design of Iterativ ASM chart and realization using ASM.

### ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN

(9)

Analysis of asynchronous sequential circuit - flow table reduction - Races - state transition table and problems in transition table- Design of asynchronous sequential circ dynamic and essential Hazards - Data synchronizers - Mixed operating mode asynchronous

### FAULT DIAGNOSIS AND TESTABILITY ALGORITHMS

Fault table method- Path sensitization method - Boolean difference method - D algorithm techniques - The compact algorithm - Fault in PLA - Test generation - DFT schemes -

### SYNCHRONOUS DESIGN USING PROGRAMMABLE DEVICES

Programming logic device families – Designing a synchronous sequential circuit using Realization of finite state machine using PLD – FPGA – Xilinx FPGA-Xilinx 4000.

| s.  fodeling in is of Finite est bench -  table, state e circuits -  ssignment- it - Static, circuits.  Tolerance fuilt in self     |

|-------------------------------------------------------------------------------------------------------------------------------------|

| s. ential  fodeling in is of Finite est bench - table, state e circuits - ssignment- it - Static, circuits.  Tolerance wilt in self |

| s. ential  fodeling in is of Finite est bench - table, state e circuits - ssignment- it - Static, circuits.  Tolerance wilt in self |

| s. ential  fodeling in is of Finite est bench - table, state e circuits - ssignment- it - Static, circuits.  Tolerance wilt in self |

| s. ential  fodeling in is of Finite est bench - table, state e circuits - ssignment- it - Static, circuits.  Tolerance wilt in self |

| s. ential  fodeling in is of Finite est bench - table, state e circuits - ssignment- it - Static, circuits.  Tolerance wilt in self |

| dodeling in is of Finite est bench - table, state e circuits - ssignment-it - Static, circuits.  Tolerance fuilt in self            |

| dodeling in is of Finite est bench - table, state e circuits - ssignment-it - Static, circuits.  Tolerance fuilt in self            |

| fodeling in is of Finite est bench - table, state e circuits - ssignment-it - Static, circuits.  Tolerance fuilt in self            |

| table, state exircuits - ssignment- it - Static, circuits.  Tolerance fuilt in self                                                 |

| table, state exircuits - ssignment- it - Static, circuits.  Tolerance fuilt in self                                                 |

| table, state exircuits - ssignment- it - Static, circuits.  Tolerance fuilt in self                                                 |

| table, state exircuits - ssignment- it - Static, circuits.  Tolerance fuilt in self                                                 |

| table, state<br>e circuits -<br>ssignment-<br>it - Static,<br>circuits.                                                             |

| essignment-<br>it - Static,<br>ccircuits.  Tolerance                                                                                |

| essignment-<br>it - Static,<br>ccircuits.  Tolerance                                                                                |

| essignment-<br>it - Static,<br>ccircuits.  Tolerance                                                                                |

| it - Static, circuits.  Tolerance suilt in self                                                                                     |

| it - Static, circuits.  Tolerance suilt in self                                                                                     |

| it - Static, circuits.  Tolerance suilt in self                                                                                     |

| Tolerance<br>wilt in self                                                                                                           |

| uilt in self                                                                                                                        |

| uilt in self                                                                                                                        |

|                                                                                                                                     |

|                                                                                                                                     |

| LA/PAL                                                                                                                              |

|                                                                                                                                     |

# LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

1

### Reference Books:

- 1. Charles H.Roth Jr "Fundamentals of Logic Design" Thomson Learning 2004, 7th edition 2014.

- 2. Nripendra N Biswas "Logic Design Theory" Prentice Hall of India,2010.

- 3. Parag K. Lala "Fault Tolerant and Fault Testable Hardware Design" B SPublications, 2002.

- 4. Parag K. Lala "Digital system Design using PLD" B S Publications, 2003.

- 5. M.D.Ciletti , Modeling, Synthesis and Rapid Prototyping with the Verilog HDL, Prentice Hall, 1999.

- 6. M.G. Arnold, Verilog Digital Computer Design, Prentice Hall (PTR), 1999.

- 7. S. Palnitkar, Verilog HDL A Guide to Digital Design and Synthesis, Pearson, 2003.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 2   | 1   | 3   | 2   | 2   | 1   | 2   | 2   | =   | (F)  | 1    |

| CO2 | 2   | 1   | 1   | 2   | 2   | 필   | 2   | 2   | -   | 201  | 1    |

| CO3 | 1   | 1   | 1   | 2   | 3   | 3   | 3   | 1   | -   | ю:   | 1    |

### 16VLPC02 DIGITAL CMOS VLSI DESIGN

L T P C 3 0 0 3

CORE/ELECTIVE COURSE: Core

### PREREQUISITES:

Basics of Digital System Design.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To learn basic concepts of MOS transistor and inverters.

- To design combinational and sequential logic circuits.

- To gain knowledge in arithmetic building blocks and memory architectures.

### **COURSE OUTCOMES:**

### Upon completion of this course, the students will have ability:

CO1:To understand basic concepts of MOS transistor and CMOS logic.

CO2:To design CMOS combinational sequential logic circuits.

CO3:Togain knowledge in arithmetic building blocks and memory architectures.

### TOPICS COVERED:

### MOS TRANSISTOR PRINCIPLES AND CMOS INVERTER

(9)

MOSFET Transistor Characteristic under Static and Dynamic Conditions, MOS Transistor Secondary Effects, CMOS Inverter - Static Characteristic, Dynamic Characteristic, Power, Energy, and Energy Delay parameters.

### COMBINATIONAL LOGIC CIRCUITS

(9)

Static CMOS Design – Complementary CMOS, Ratioed Logic, Pass-Transistor Logic. Dynamic CMOS Design – Dynamic Logic: Basic Principles, Speed and Power Dissipation of Dynamic Logic, Issues in Dynamic Design, Cascading Dynamic Gates.

### SEQUENTIAL LOGIC CIRCUITS

(9)

Timing metrics for sequential circuits, Static Latches and Registers, Dynamic Latches and Registers, Pipelines, Pulse and sense amplifier based Registers, Non-Bistable Sequential Circuits.

### ARITHMETIC BUILDING BLOCKS AND MEMORY ARCHITECTURES

(9)

Data path circuits, Architectures for Adders, Multipliers, Shifters, Speed and Area Tradeoffs, Array Subsystems: SRAM, DRAM, ROM.

### ARCHITECTURE DESCRIPTION

(9)

Introduction, Power distribution, Input/Output, Clock, Hardware Description Languages, Verilog HDL: Behavioral modeling, Structural gate modeling, Switch modeling, Basic constructs, FSM, High-level synthesis.

## LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. Jan M Rabaey, Anantha Chandrakasan, B Nikolic, Digital Integrated Circuits: A Design Perspective, Second Edition, 2003, Prentice Hall of India.

- 2. Niel H.E. Weste, David Harris, Ayan Banerjee, CMOS VLSI Design- A circuits and Systems Perspective, Third Edition, 2013, Pearson education.

- Chris Spear, System verilog for Verification, Springer, 2006.

Wayne Wolf, Modern VLSI Design, PHI Learning Private Limited, New Delhi, 2011.

- 5. Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits, McGraw Hill, 3rd Edition, 2011.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 3   | 3   | 3   | 2   | 2   | 1   | 8   | #   | 1   | -    | =    |

| CO2 | 3   | 2   | 3   | 2   | 1   | -   | 1   | -   | -   | -    | 1    |

| CO3 | 3   | 3   | 2   | 2   | 2   | 1   | 1   | 2   | 1   | =    | 1    |

### 16VLPC03 VLSI DESIGN AUTOMATION

L T P C 3 0 0 3

### CORE/ELECTIVE COURSE: Core

### **PREREQUISITES:**

Data Structures.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To acquire knowledge on VLSI Design methodologies & CAD tools.

- To analyze the design trade off in various partitioning, placement and floor planning in VLSI Design Automation.

- To analyze the different global routing Algorithm and acquire knowledge about logical synthesis.

### **COURSE OUTCOMES:**

### Upon completion of this course, the students will have:

- CO1: Knowledge on VLSI Design methodologies & CAD tools.

- CO2: An ability to analyze the design trade off in various partitioning, placement and floor planning in VLSI Design Automation.

- CO3: An ability to analyze the different global routing Algorithm and acquire knowledge about logical synthesis.

### **TOPICS COVERED**

### **VLSI DESIGN METHODOLOGIES**

(9)

Introduction to VLSI Design Methodologies: VLSI Design Cycle - New trends in VLSI design Cycle-Physical Design - New trends in physical design cycle - Design styles - VLSI Design Automation Tools - Algorithmic graph theory and computational complexity - Tractable and intractable problems.

### **PARTITIONING & PLACEMENT**

(9)

(9)

Partitioning – Problem formulation – Group migration Algorithms – KL,FM Algorithms, Placement – Simulation based algorithm – Simulated annealing, Force directed algorithm, Partition based algorithms – Breuer's Algorithm, Terminal propagation Algorithm, Floor planning – Slicing floor plan, Constrained Based Floor planning – Pin assignment.

ROUTING

Routing - Grid routing - Maze routing Algorithms, Global routing - Shortest path based Algorithm, Steiner free based Algorithm, Detailed routing - Left edge Algorithm, Greedy channel Routing - Over the cell routing, clock routing.

SIMULATION (9)

Simulation – Gate level modeling and Simulation – Switch level modeling and simulation – Switch level modeling and simulation - Combinational Logic Synthesis – Binary decision diagrams – Two level logic Synthesis.

### MODELING AND SYNTHESIS

(9

High level synthesis – Hardware models – Internal representation – Allocation assignment and scheduling – High level transformation.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

1.N.A Sherwani, "Algorithms for VLSI Physical Design Automation", Kluwer Academic Publishers, 2007

2.S.H. Gerez, "Algorithms for VLSI Design Automation", John Wiley & Sons, 2008.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 2   | 3   | 2   | 2   | 3   | 2   | 1   | 2   | 3   | 3    | =    |

| CO2 | 2   | 3   | 2   | 2   | 3   | 2   | 1   | 2   | 3   | 3    | 5    |

| CO3 | 2   | 3   | 2   | 2   | 3   | 3   | 1   | 3   | 3   | 3    | 2    |

### 16VLPC04 VLSI DESIGN LABORATORY

0

### CORE/ELECTIVE COURSE: Core

### PREREQUISITES:

VLSI

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To acquire Knowledge on modelling and synthesis of digital system design using HDL programming languages.

- To Implement the design using FPGA/CPLD devices.

- To get exposure to critical path time calculations and RTL modules.

### **COURSE OUTCOMES:**

### Upon completion of the course, the students will have:

CO1: Knowledge on modelling and synthesis of digital system design using HDL programming languages.

CO2: Ability to design using FPGA/CPLD devices.

CO3:An exposure to critical path time calculations and RTL modules.

### **TOPICS COVERED**

### **VLSI Front End Design programs**

Programming can be done using any HDL complier, Verification of the Functionality module using functional Simulator, Timing Simulation for Critical Path time Calculation, Synthesis module, Place & Route and implementation of design using FPGA/CPLD Devices.

- 1. Design and Simulation of Half and Full adders, Serial Binary Adder, Multi Precision Carry Look Ahead Adder.

- 2. Design of 4-bit binary, BCD counters (synchronous/ asynchronous reset).

- 3. Design of a N- bit shift register of Serial- in Serial out, Serial in parallel out, Parallel out and Parallel in Parallel Out.

- 4. Design of Sequence Detector (Finite State Machine- Mealy and Moore Machines).

- 5. Design of 4- Bit Multiplier and 4-bit Divider.

- 6. Design of ALU to Perform ADD, SUB, AND, OR, 1's compliment, 2's Complimen Multiplication and Division.

- 7. Design of Finite State Machine.

- 8. System Implementation (LCD Interfacing / Keypad Interfacing)

- 9. Design of Memories

LECTURE: 0 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 60 PERIODS TOTAL: 60 PERIODS

| T P C 0 4 2 |  |

|-------------|--|

|             |  |

|             |  |

|             |  |

|             |  |

|             |  |

|             |  |

|             |  |

| y of the    |  |

| Adder,      |  |

| in Serial   |  |

| m Schal     |  |

| pliment,    |  |

|             |  |

|             |  |

| <i>,</i>    |  |

| ,           |  |

### Reference Books:

- 1. Charles Roth Jr.H., "Fundamentals of Logic Design", Australia cengage learning,2014,7th edition.

- 2. Samir Palnitkar, "Verilog HDL-A guide to Digital Design and synthesis second edition Pearson", Education in South Asia 2013.

- 3. "The design warrior guide to FPGA's, devices, Tools and flows". Clive Maxfield,2011.

- 4. Altera Corporation-"Standard Cell ASIC to FPGA Design Methodology and Guidelines", April 2009.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8      | PO9      | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|----------|----------|------|------|

| CO1 | 3   | 3   | 2   | 3   | 2   | =   | 3   | <u> </u> | =        | *    | *    |

| CO2 | 3   | 3   | 2   | 3   | 2   | -   | 3   | +        | =        |      | =    |

| CO3 | 3   | 3   | E   | 2   | 2   | =   | 3   | 2        | <u>-</u> | 2    | 2    |

### 16VLPC05 ANALOG VLSI

L T P C 3 0 0 3

### CORE/ELECTIVE COURSE: Core

### PREREQUISITES:

Digital CMOS VLSI design.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To understand analog transistor fundamentals, circuits and amplifiers of CMOS FET.

- To gain knowledge analog filters and converters.

- To test the analog circuits and to apply their knowledge to build common analog blocks.

### **COURSE OUTCOMES:**

### Upon completion of this course, the students will be able to:

- CO1:Understand analog transistor fundamentals, circuits and amplifiers of CMOS FET.

- CO2:Gain knowledge analog filters and converters.

- CO3:Test the analog circuits and to apply their knowledge to build common analog blocks.

### TOPICS COVERED

### BASIC MOS DEVICE PHYSICS

(9)

MOS Device Models- Review of Small Signal MOS Transistor Models-basic CMOS circuits-basic gain stage –super MOS transistor –Primitive analog cells - BICMOS Technology- fabrication, layout, design rules-Passive IC components: capacitor, resistor, inductor, transformer.

### **BASIC ANALOG CIRCUITS AND AMPLIFIERS:**

(9)

Current sources and sinks - Current mirrors/amplifiers - Voltage and current references, Comparator, Multiplier. AMPLIFIERS- MOS and BJT inverting amplifier - Improving performance of inverting amplifier - CMOS and BJT differential amplifiers - Characterization of Op-Amp - The BJT two stage opamp - The CMOS two stage op-amp op-amps with output stage, Folded cascode op-amp, Transconductance Amplifier- Instrumentation amplifier.

### NOISE AND FILTERS:

(9)

Noise Spectrum, Sources, Types, Thermal and Flicker noise, Representation in circuits, Noise Bandwidth, Noise Figure. Low pass filters - High pass filters - Band Pass filters - Switched capacitor filters - Phase Locked Loops.

### D/A AND A/D CONVERTERS:

(9)

Ideal A/D and D/A converters, Quantization noise, Signed codes, Performance limitations. D/A converter: Current scaling, Voltage scaling and Charge scaling D/A converters - Serial D/A converters - Serial A/D converters, Parallel - High performance A/D converters.

### ANALOG VLSI TESTING AND SYSTEMS:

(9)

FAULT modelling and simulation - BIST - Analog VLSI for Vision - System Design Issues - An Integrated Image Acquisition, Smoothing and Segmentation Focal Plane Processor.

# LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. Behzad Razavi, **Design of Analog CMOS Integrated Circuits**, McGraw Hill, 2<sup>nd</sup> Edition 2002.

- 2. Gray, P.R., Hurst, P.J., Lewis, S.H., and Meyer, R.G., Analysis and Design of Analog Integrated Circuits, John Wiley, 5<sup>th</sup> Edition, 2001.

- 3. Mohammed Ismail, Analog VLSI signal and Information processing, McGraw-Hill, 1994.

- 4. John L. Wyatt et.al, Analog VLSI Systems for Image Acquisition and Fast Early Vision Processing, International Journal of Computer Vision.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9  | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| CO1 | 3   | 2   | 3   | 2   | 3   | 2   | 1   | (m) | -    | 2    | 8    |

| CO2 | 3   | 3   | 2   | 3   | 2   | 1   | 2   | -   | 35   | 1    | ·    |

| CO3 | 3   | 3   | 3   | 2   | 1   | 1   | 1   | (40 | (ex) | 2    |      |

#

CORE/ELECTIVE COURSE: Core

### PREREQUISITES:

Digital CMOS VLSI design.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To be aware of power consumption, power dissipation in CMOS device and get exposed to logic level power optimization.

- To gain Knowledge on low power design and power estimation techniques in CMOS circuits.

- To Understand the synthesis and software design for low power .

### **COURSE OUTCOMES:**

### Upon completion of the course, the students will have:

- CO1: Awareness of power consumption, power dissipation in CMOS device and get exposed to logic level power optimization.

- CO2:Knowledge on low power design and power estimation techniques in CMOS circuits.

- CO3:Understanding of the synthesis and software design for low power.

### **TOPICS COVERED:**

### **POWER DISSIPATION IN CMOS**

(9)

Hierarchy of limits of power – Sources of power consumption – Physics of power dissipation in CMOS FET devices- Basic principle of low power design.

### **POWER OPTIMIZATION**

(9)

Logical level power optimization – Circuit level low power design – Circuit techniques for reducing power consumption in adders and multipliers.

### **DESIGN OF LOW POWER CMOS CIRCUITS**

(9)

Computer Arithmetic techniques for low power systems – Reducing power consumption in memories – Low power clock, Interconnect and layout design – Advanced techniques – Special techniques.

### **POWER ESTIMATION**

(9)

Power estimation techniques – Logic level power estimation – Simulation power analysis – Probabilistic power analysis.

### SYNTHESIS AND SOFTWARE DESIGN FOR LOW POWER

(9)

Synthesis for low power —Behavioral level transforms- Software design for low power.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. K.Roy and S.C. Prasad, "Low Power CMOS VLSI" circuit design, Wiley, 2009.

- 2. Dimitrios Soudris, Chirstian Pignet, Costas Goutis, "Designing CMOS circuits for low power", Springer US 2010.

- 3. B. Kuo and J.H Lou, "Low voltage CMOS VLSI Circuits", Wiley 2014.

- 4. Gary K.Yeap, "Practical Low Power Digital VLSI Design", Springer Science and business media, 2012.

- 5. James B. Kuo, Shin chia Lin, Low voltage "SOI CMOS VLSI" Devices and Circuits. John Wiley and sons, inc2004.

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7            | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|----------------|-----|-----|------|------|

| CO1 | 3   | 2   | 2   | 2   | 2   | -   | ) <del>-</del> | =   | 2   | E    | =    |

| CO2 | 3   | 2   | -   | 2   | 2   | -   | -              | -   | 2   | ::€  | *    |

| CO3 | 2   | 2   | 2   | E   | 3   | 20  | 2              | 1   | 2   | 1/2/ | 2    |

Controller of Examinations

Gevernment 10 to a of Technology

COIMBATURE - 641 013

|                                 | L | T | P | C |  |

|---------------------------------|---|---|---|---|--|

| 16VLPC07 VLSI SIGNAL PROCESSING | 3 | 0 | 0 | 3 |  |

### CORE/ELECTIVE COURSE: Core

### **PREREQUISITES:**

- Digital signal processing.

- VLSI Architecture.

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVE:**

- To improve the performance of the existing FIR filter structures to suit VLSI designs.

- To design efficient IIR filter structures and Bit level architectures suitable for VLSI Designs.

- To modify the clocking styles, synchronous and Asynchronous protocols suitable for VLSI Architectures.

### **COURSE OUTCOMES:**

### Upon completion of this course the students will have:

CO1: Ability to improve the performance of the existing FIR filter structures to suit VLSI designs.

CO2: Ability to design efficient IIR filter structures and Bit level architectures suitable for VLSI designs.

CO3: Ability to modify the clocking styles, synchronous and Asynchronous protocols suitable for VLSI Architectures.

### TOPICS COVERED:

# INTRODUCTION TO DSP SYSTEMS, PIPELINING AND PARALLEL PROCESSING OF FIR FILTERS (9)

Introduction to DSP systems – Typical DSP algorithms, Data flow and Dependence graphs - critical path, Loop bound, iteration bound, Longest path matrix algorithm, Pipelining and Parallel processing of FIR filters, Pipelining and Parallel processing for low power.

### RETIMING, ALGORITHMIC STRENGTH REDUCTION (9)

Retiming – definitions and properties, Unfolding – an algorithm for unfolding, properties of unfolding, sample period reduction and parallel processing application, Algorithmic strength reduction in filters and transforms – 2-parallel FIR filter, 2-parallel fast FIR filter, DCT architecture, rank-order filters, Odd-Even merge-sort architecture, parallel rank-order filters.

# FAST CONVOLUTION, PIPELINING AND PARALLEL PROCESSING OF IIR FILTERS

Fast convolution – Cook-Toom algorithm, modified Cook-Toom algorithm, Pipelined and parallel recursive filters – Look-Ahead pipelining in first-order IIR filters, Look-Ahead pipelining with power-of-2 decomposition, Clustered look-ahead pipelining, Parallel processing of IIR filters, combined pipelining and parallel processing of IIR filters.

### **BIT-LEVEL ARITHMETIC ARCHITECTURES**

(9)

Bit-level arithmetic architectures – parallel multipliers with sign extension, parallel carry-ripple and carry-save multipliers, Design of Lyon's bit-serial multipliers using Horner's rule, bit-serial FIR filter CSD representation, CSD multiplication using Horner's rule for precision improvement, Distributed Arithmetic fundamentals and FIR filters.

# NUMERICAL STRENGTH REDUCTION, SYNCHRONOUS, WAVE AND ASYNCHRONOUS PIPELINING (9)

Numerical strength reduction – subexpression elimination, multiple constant multiplication, iterative matching, synchronous pipelining and clocking styles, clock skew in edge-triggered single phase clocking, two-phase clocking, wave pipelining, Asynchronous pipelining, bundled data versus dual rail protocol.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. Keshab K. Parhi, "VLSI Digital Signal Processing Systems, Design and implementation", Wiley Interscience, 2007.

- 2. U. Meyer Baese, "Digital Signal Processing with Field Programmable Gate Arrays", Springer Second Edition, 2004.

- 3. Kung S. Y, H. J. While House, T. Kailath, "VLSI and Modern Signal Processing", Prentice Hall, 1985.

- 4. Jose E. France, Yannis Tsividis "Design of Analog Digital VLSI Circuits for Telecommunications and Signal Processing", Prentice Hall, 1994.

- 5. Medisetti V. K, "VLSI Digital Signal Processing", IEEE Press (NY), USA, 1995...

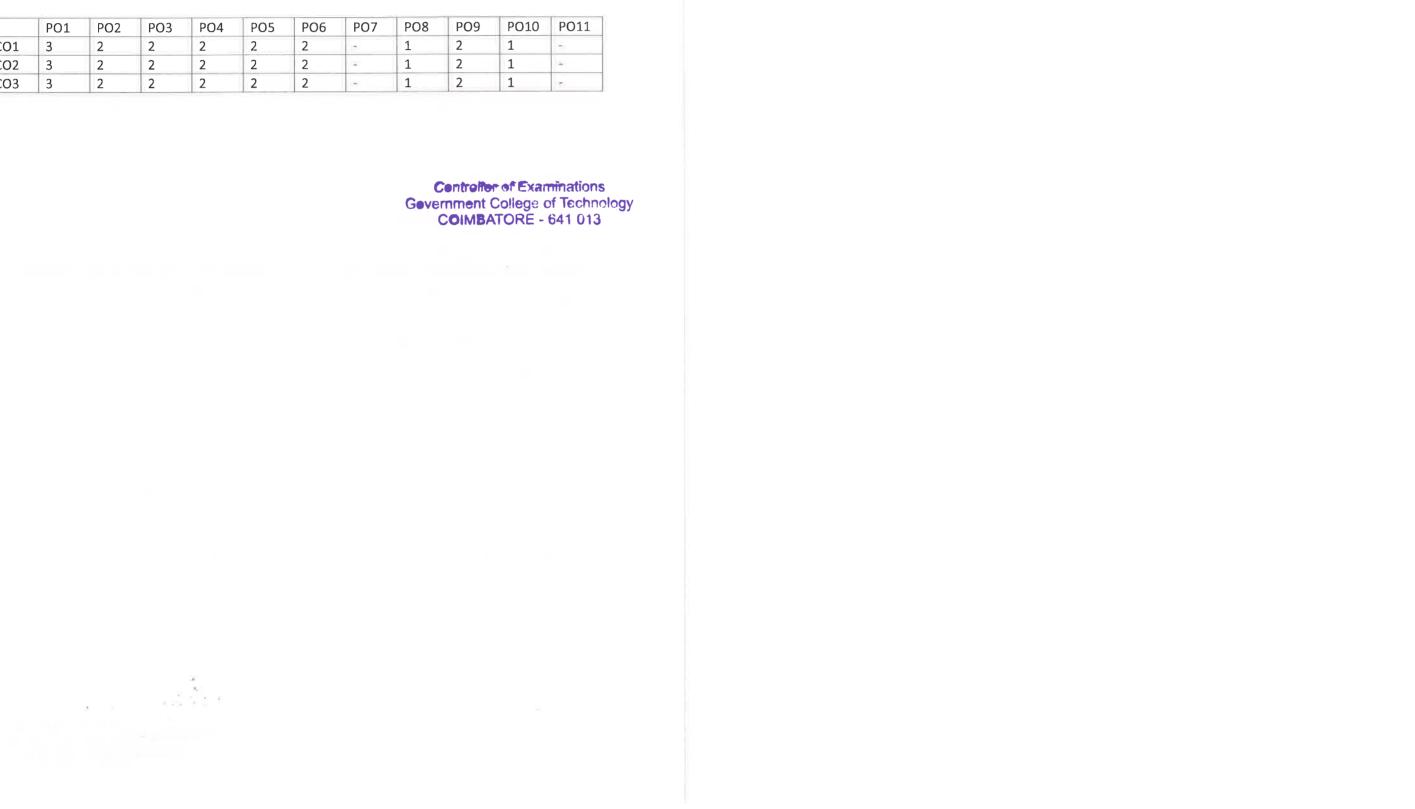

|     | PO1 | PO2    | PO3 | PO4      | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|--------|-----|----------|-----|-----|-----|-----|-----|------|------|

| CO1 | 2   |        | 1   | U.S.     | 1   | 1   | 2   | 1   | 1   | 170  | -    |

| CO2 | 2   | (e.e.) | 1   | : = :    | 1   | 1   | 1   | Э   | er  |      | 1    |

| CO3 | 2   | -      | 1   | <b>S</b> | 1   | 1   | 8   | 1   | 31  |      | 1    |

Gevernment College of Technology

COIMBATORE - 641 013

| pple and<br>IR filter,<br>stributed |  |

|-------------------------------------|--|

| stributed                           |  |

| ONOUS                               |  |

| iterative                           |  |

| le phase<br>dual rail               |  |

|                                     |  |

|                                     |  |

|                                     |  |

| ", Wiley,                           |  |

| Springer,                           |  |

| Prentice                            |  |

| nications                           |  |

|                                     |  |

|                                     |  |

| PO11                                |  |

| 1                                   |  |

| 1                                   |  |

|                                     |  |

| tiens<br>chnology<br>013            |  |

| 013                                 |  |

|                                     |  |

|                                     |  |

|                                     |  |

|                                     |  |

|                                     |  |

|                                     |  |

### 16VLPC08 ASIC DESIGN

L T P C 3 0 0 3

### CORE/ELECTIVE COURSE: Elective

### PREREQUISTES:

VLSI Technology.

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES**

- To Gain the fundamentals of ASIC design.

- To Gain Knowledge on programmable ASIC s.

- To Gain Knowledge in the logical synthesis, simulation and testing aspects of ASIC

### **COURSE OUTCOMES:**

### After completing this course, the students will have:

CO1: Sufficient theoretical knowledge for carrying out the ASIC design.

CO2: Knowledge about programmable ASIC s.

CO3:Knowledge in the logical synthesis, simulation and testing

aspects of ASIC.

### **TOPICS COVERED:**

### OVERVIEW OF ASIC AND PLD

(9)

Types of ASICs - Design flow - CAD tools used in ASIC Design - Programming Technologies: Antifuse - static RAM - EPROM and EEPROM technology, Programmable Logic Devices: ROMs and EPROMs - PLA - PAL. Gate Arrays - CPLDs and FPGA.

### PROGRAMMABLE ASIC s

(9)

Programmable ASIC cells for ACTEL and XILNX -DC & AC inputs and outputs-ACTEL and XILINX-programmable ASIC architecture-Clock and Power inputs – Architecture and I/O blocks -XILINX XC 4000- FLEX 8000/10000, ACTEL's ACT-1,2,3 and their speed performance, Altera MAX 5000 and 7000 - Altera MAX 9000 – Spartan II and Virtex II FPGAs - Apex and Cyclone FPGAs.

### ASIC PHYSICAL DESIGN

(9)

System partition Partitioning - Partitioning methods - Interconnect delay models and measurement of delay - Floor planning - Placement - Routing : Global routing - Detailed routing - Special routing.

### LOGIC SYNTHESIS, SIMULATION AND TESTING

(9)

Design systems Logic Synthesis - Verilog and VHDL synthesis - Types of simulation -Boundary scan test - Fault simulation - Automatic test pattern generation.

### HIGH PERFORMANCE ALGORITHMS FOR ASICS/ SOCS.

(9)

DAA and computation of FFT and DCT. High performance filters using delta-sigma modulators. Case Studies: Digital camera, SDRAM, High speed data standards.

# LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. M.J.S.Smith, "Application Specific Integrated Circuits", Pearson, 200

- 2. Steve Kilts, "Advanced FPGA Design," Wiley Inter-Science.

- 3. Roger Woods, John McAllister, Dr. Ying Yi, Gaye Lightbod, "FPGA-based Implementation of Signal Processing Systems", Wiley, 2008.

- 4. Mohammed Ismail and Terri Fiez, "Analog VLSI Signal and Information Processing", Mc Graw Hill, 1994.

- 5. Douglas J. Smith, HDL Chip Design, Madison, AL, USA: Doone Publications, 1996.

6. Jose E. France, Yannis Tsividis, "Design of Analog Digital VLSI Circuits for Telecommunication and Signal Processing", Prentice Hall, 1994.

|     | PO1 | PO2 | PO3 | PO4 | PO5  | PO6     | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|------|---------|-----|-----|-----|------|------|

| CO1 | 1   | -   | -   | -   |      | 9#E 100 | 2   | 2   | 2   | 2    | 3    |

| CO2 | 3   | 2   | 2   | 1   | 1    | *       | -   | 2   | 2   | 2    | 3    |

| CO3 | 1   | 3   | =   | 920 | 1124 | -       | 2   | 2   | 2   | 2    | 3    |

### 16VLPC09 SYSTEM LEVEL DESIGN LABORATORY

L T P C 0 4 2

### CORE/ELECTIVE COURSE: core

### **PREREQUISITES:**

- Analog IC Design.

- Digital CMOS VLSI Design.

- Advanced Digital System Design.

### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To analyze analog, digital and mixed signal circuits.

- To gain knowledge on different facets of VLSI design using CAD tools.

- Hands on experience on VLSI based experiments using simulation and synthesis tools.

### **COURSE OUTCOMES:**

### At the end of the course the student will be able to/ have an:

CO1: Analyze analog, digital and mixed signal circuits.

CO2:Gain knowledge on different facets of VLSI design using CAD tools.

CO3:Hands on experience on VLSI based experiments using simulation and synthesis tools.

### TOPICS COVERED:

### Analog Circuits:

- 1. AN INVERTER

- 2. MOS DIFFERENTIAL AMPLIFIER

- 3. COMMON SOURCE AMPLIFIER & COMMON DRAIN AMPLIFIER

- 4. OPERATIONAL AMPLIFIER

### Mixed Signal Circuits:

- 5. R-2R DAC

- 6. SAR BASED ADC

- 7. PLL

### Digital Signal/Circuits:

- 8. GCD-computer (4-bit)

- 9. Booth multiplier (4-bit)

- 10. 4-pt FFT/IFFT

### Hardware Co-Simulation using FPGA kits:

- 11. CORDIC for Sin  $\Theta/\text{Cos }\Theta$  & Sin<sup>-1</sup> $\Theta/\text{Cos}^{-1}\Theta$

- 12. Adders & Multipliers

- 13. Edge Detection

Tools: CADENCE / TANNER /Mentor/Synopsis/HDL Simulation and Synthesis tools.

LECTURE: 0 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 60 PERIODS TOTAL: 60 PERIODS

|                   | 1   |

|-------------------|-----|

|                   |     |

|                   | 1   |

|                   | -   |

|                   |     |

|                   |     |

|                   | -   |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

| s.                |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

| s tools.          |     |

|                   | -   |

|                   | 1   |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   | 4   |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

| ynthesis tools.   | 1   |

| J.1.110010 10010. |     |

|                   |     |

|                   |     |

|                   |     |

|                   |     |

|                   | a . |

### References Books

- 1. Behzad Razavi, **Design of Analog CMOS Integrated Circuits**, McGraw Hill, 2<sup>nd</sup> Edition 2002.

- 2. Gray, P.R., Hurst, P.J., Lewis, S.H., and Meyer, R.G., Analysis and Design of Analog Integrated Circuits, John Wiley, 5<sup>th</sup> Edition, 2001.

- 3. Samir Palnitkar, Verilog HDL-A Guide to digital design and synthesis, 2<sup>nd</sup> Edition, Pearson Education, 2013.

- 4. System Generator for DSP User Guide, 2012.

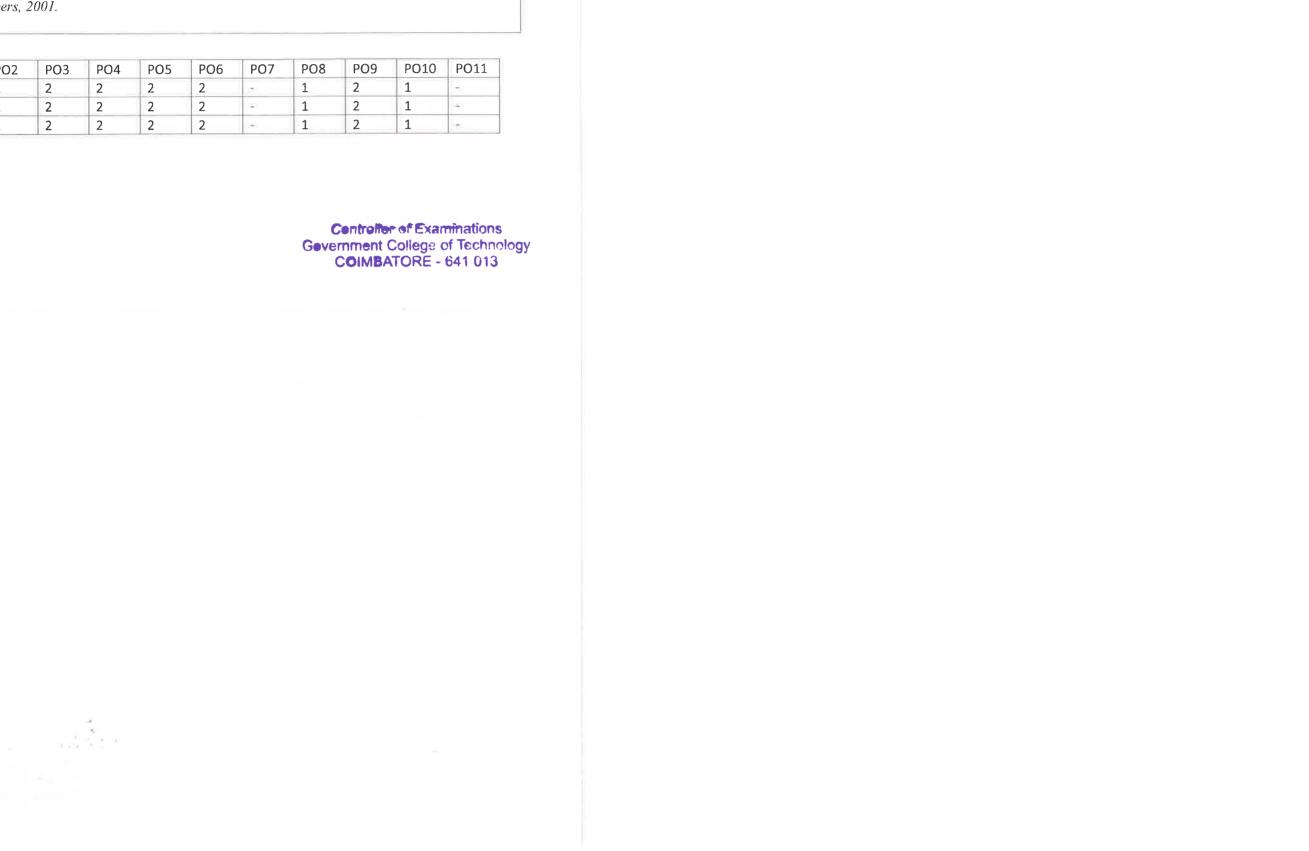

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 3   | 2   | 2   | 2   | 2   | Ξ.  | 1   | ¥   | ¥   | =    | 1    |

| CO2 | 2   | 3   | 2   | 1   | 3   | н   | -   | Ħ   | +   | .=   | -    |

| CO3 | 2   | 1   | 2   | 3   | 3   | Ē   | ê   | 1   | 2   | 2    | 2    |

# 16VLPE01 IMAGE AND VIDEO PROCESSING (Common to Applied Electronics)

L 3

T 0

P C 3

CORE/ELECTIVE COURSE: Elective

### PREREQUISITES:

• Digital Signal Processing.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To gain knowledge on the basics of digital imaging.

- To get exposure to various image processing techniques.

- To get exposure to video processing.

### **COURSE OUTCOMES:**

### Upon completion of this course, the students will have:

CO1: Knowledge on the basics of digital imaging.

CO2: Exposure to various image processing techniques.

CO3: Exposure to video processing.

### TOPICS COVERED:

### DIGITAL IMAGE PROCESSING FUNDAMENTALS

(9)

Image Processing Systems- Elements of visual perception- Image sensing and acquisition- Image sampling and quantization. Pixel relationships- Statistical properties- Histogram, mean, Standard deviation-. Color Image Fundamentals, Chromaticity diagram. Color models- Image file formats, Image transforms, Discrete fourier transform- Discrete cosine transform- wavelet transform.

### IMAGE ENHANCEMENT AND RESTORATION

(9)

Enhancement in spatial domain- Basic gray level transforms- Histogram processing- Spatial Filtering-Enhancement in frequency domain- Image restoration- Degradation model- Noise models- Spatial Filters-Frequency domain filters.

### IMAGE SEGMENTATION AND REPRESENTATION

(9)

Detection of discontinuities- Point, Line and Edge detection- Gradient operators- Thresholding- Region based segmentation- Representation schemes- Chain codes- Polygon approximation- Boundary descriptors- Simple descriptors- Shape number- Fourier descriptors.

### VIDEO FUNDAMENTALS

(9)

Basic concepts and Terminology-Monochrome Analog video – Color in Video – Analog video standards – Digital video basics – Analog-to Digital conversion – Color representation and chroma sub sampling – Digital video formats and standards Video sampling rate and standards conversion.

### VIDEO OBJECT EXTRACTION

(9)

Back ground subtraction – Frame difference – Static and dynamic background modeling – Optical flow techniques – Handling occlusion – Scale and appearance changes – Shadow removal.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. Rafael C. Gonzalez, Richard E. Woods, "Digital Image Processing", Pearson Education, Inc., Second Edition, 2004.

- 2. Anil K. Jain, "Fundamentals of Digital Image Processing", Prentice Hall of India, 2002.

- 3. Oges Marques, "Practical Image and Video Processing Using MATLAB", Wiley-IEEE Press, 2011.

- 4. A.Bovik, "Handbook of Image and Video processing", 2<sup>nd</sup> Edition, Academic press, 2005.

- 5. Mark Nixon and Alberto Aguado, "Feature Extraction and Image Processing", Academic Press, 2008.

- 6. Rafael C. Gonzalez, Richard E. Woods, Steven Eddins, "Digital Image Processing using MATLAB", Pearson Education, Inc., 2004.

- 7. Jayaraman S, Esakkirajan S and Veerakumar J, "Digital Image Processing", Tata McGraw Hill Education pvt ltd, 2010.

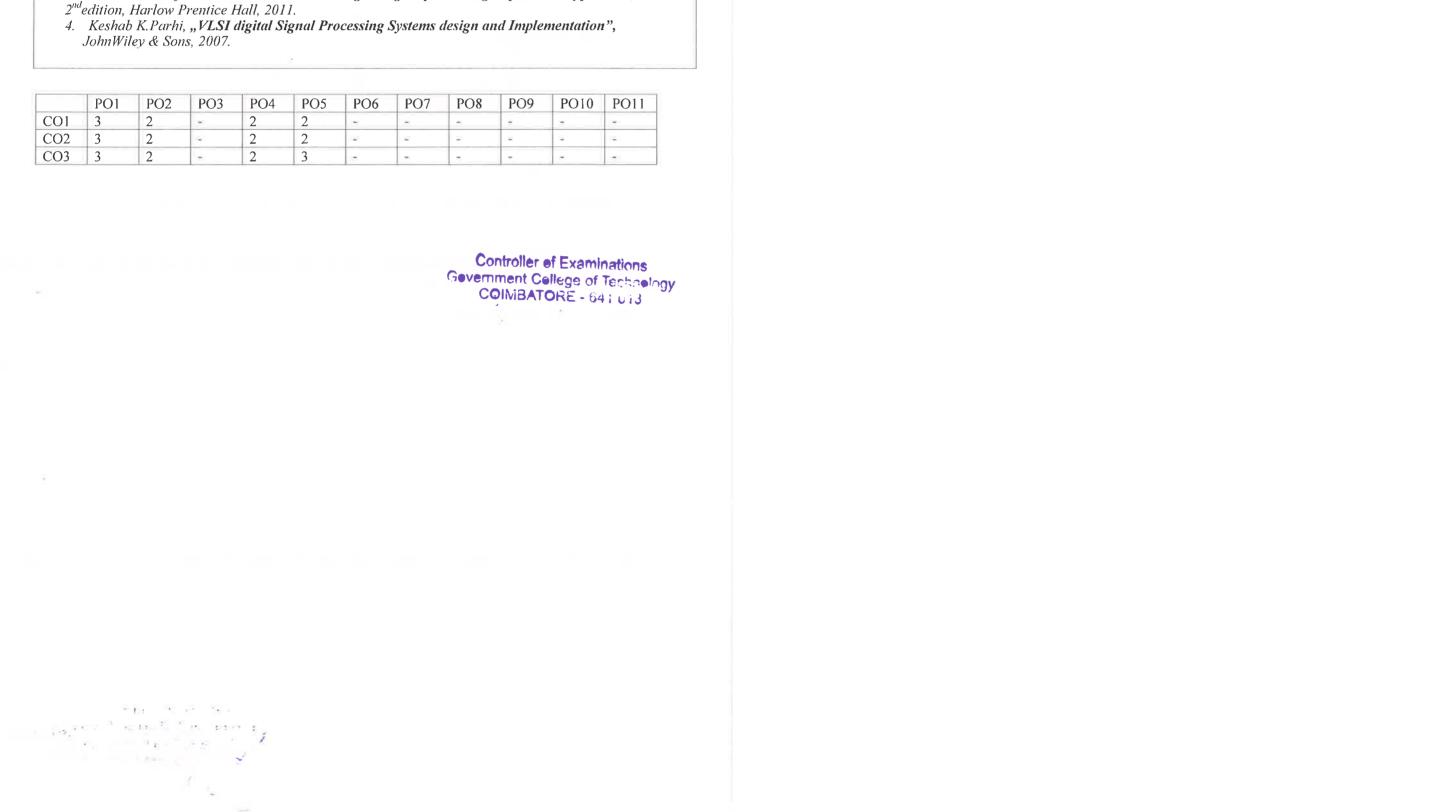

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 2   | 3   | 2   | 2   | 3   | 2   | 1   | 1   | 1   | 3    | 20   |

| CO2 | 3   | 3   | 2   | 2   | 3   | 3   | 1   | 1   | 3   | 3    | (4)  |

| CO3 | 3   | 3   | 2   | 2   | 3   | 3   | 1   | 1   | 3   | 3    | 2/   |

| 16VLPE02                        | MIXED SIGNAL CIRCUITS AND INTERFACING |  |  |  |  |  |  |  |

|---------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| (Common to Applied Electronics) |                                       |  |  |  |  |  |  |  |

### CORE/ELECTIVE COURSE: Core

### **PREREQUISITES:**

• A-D & D-A Converters.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To gain basic knowledge on Sample and Hold Architecture.

- To acquire knowledge on various A-D & D-A converters Architecture.

- To gain Knowledge on Building Blocks & Precision Techniques.

### **COURSE OUTCOMES:**

### Upon completion of this course the students will have:

- CO 1: Basic knowledge on Sample and Hold Architecture.

- CO 2: Knowledge on various A-D & D-A converters Architecture.

- CO 3: Knowledge on Building Blocks & Precision Techniques.

### TOPICS COVERED:

### SAMPLE-AND-HOLD ARCHITECTURES

Introduction to Data conversion and Processing- Sampling Switches-MOS, Diode Switches-Improvements in MOS Switch Performance-Conventional Open-Loop and Closed-Loop Arc Open-Loop Architecture with Miller Capacitance, Multiplexed-Input Architectures, Recyclin Architecture, Switched-Capacitor Architecture, Current-Mode Architecture.

### DIGITAL-TO-ANALOG CONVERTER ARCHITECTURES

Basic principles-General Considerations-Performance Metrics-Reference Multiplication and Switching and Logical Functions in DACs-Resistor-Ladder DAC Architectures, Current-Ste Architectures.

### ANALOG-TO-DIGITAL CONVERTER ARCHITECTURES

General Considerations- Performance Metrics- Flash Architectures, Two-Step Architectures, Interpolative and Folding Architectures, Pipelined Architectures, Successive Approximation Architectures, Interleaved Architectures.

### BUILDING BLOCKS OF DATA CONVERSION SYSTEMS

Amplifiers- Open-Loop Amplifiers, Closed-Loop Amplifiers, Operational Amplifiers, Gain Techniques, Common-Mode Feedback. Comparators- Bipolar Comparators, CMOS Compa

> Controller of Exa Government College COIMBATORE - 64

| L T 3 0    | P C     |

|------------|---------|

| 3 0        | P C 0 3 |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            |         |

|            | (9)     |

|            |         |

|            |         |

| chitectur  | e,      |

| ng         | _       |

| D          |         |

|            |         |

|            | (0)     |

|            | (9)     |

| l Division | n       |

|            | 11-     |

| ering      |         |

|            |         |

|            | (6)     |

|            | (9)     |

|            |         |

| ,          |         |

| l          |         |

|            |         |

|            |         |

|            | (9)     |

|            | . /     |

| Boosting   | g       |

| rators,    |         |

| ,          |         |

| - In asime | ns      |

| of Tech    | neleg   |

| 01 1601    | 13      |

BiCMOS Comparators.

### PRECISION TECHNIQUES

(9)

Comparator Offset Cancellation- Input, Output and multistage Offset Storage, Comparators Using Offset-Cancelled Latches- Op Amp Offset Cancellation- Calibration Techniques- DAC and ADC Calibration Techniques.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. BehzadRazavi, "Principles of Data Conversion System Design", JohnWiley & Sons, 2011.

- 2. Sundaram Natarajan, "Microelectronics Analysis & design", McGrawHill2006.

- 3. R.JBaker, "CMOS Mixed Signa lCircuit Design", Wiley Interscience, 2<sup>nd</sup> Edition, 2009.

- 4. B.Razavi, "Design of Analog CMOS Integrated Circuits", McGrawHill, 2005.

- 5. DavidA. Johns and Ken Martin, "Analog Integrated Circuit Design", WileyIndia, 2008.

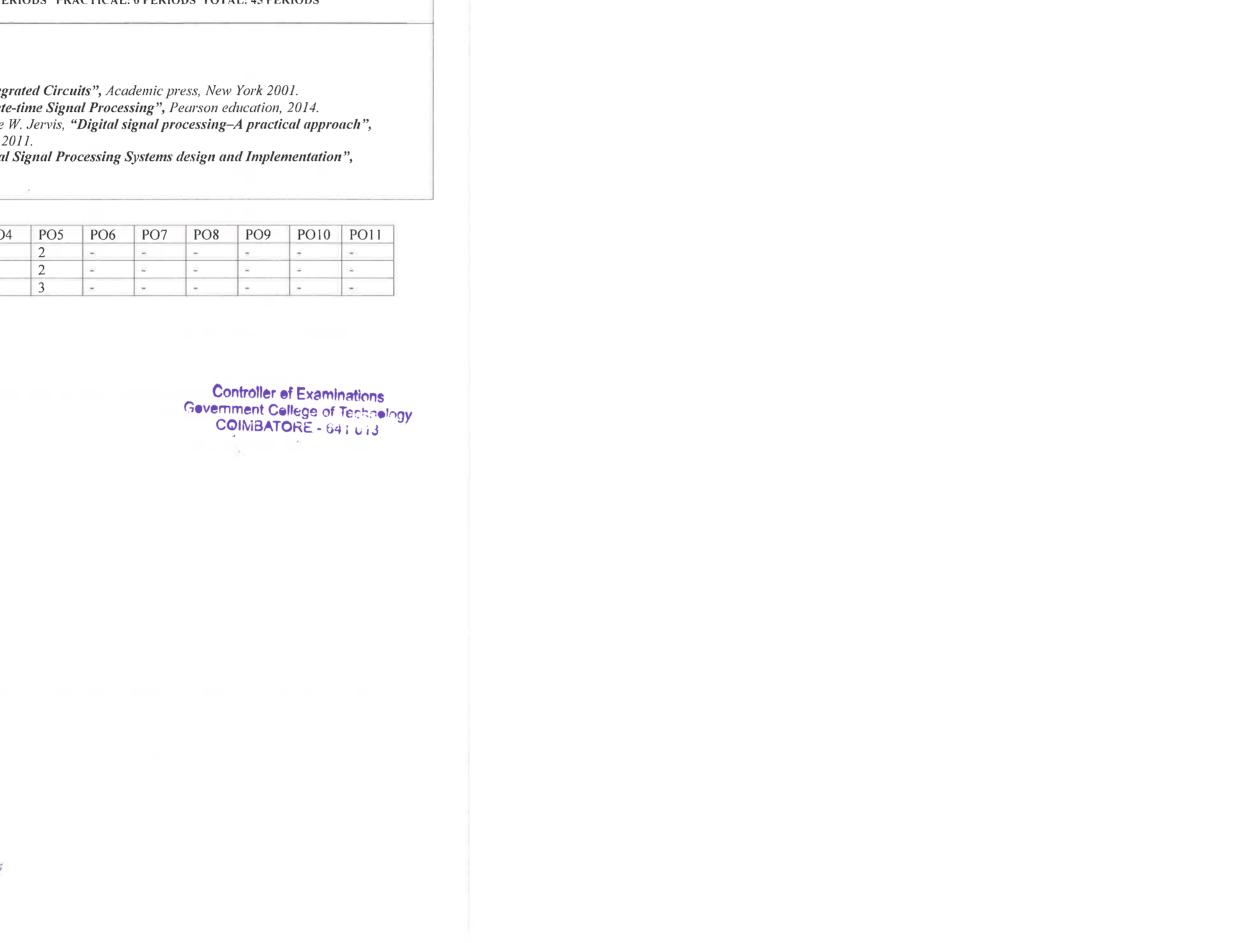

|     | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|

| CO1 | 3   | 1   | 2   | 2   | 2   | 2   | 2   | 1   | 1   | 2    | 2    |

| CO2 | 3   | 9   | 2   | -   | 90  | H   | -   | 197 |     | 126  | (2)  |

| CO3 | 3   | 3   | 1   |     | 2   | 7   | 1   | 7   | 1   | -    | ₩.   |

|                                 | L | T | P | ( |

|---------------------------------|---|---|---|---|

| 16VLPE03 RF SYSTEM DESIGN       | 3 | 0 | 0 | 3 |

| (Common to Applied Electronics) |   | 1 |   |   |

CORE/ELECTIVE COURSE: Elective

### **PREREQUISITES:**

Transmission Lines, RF System.

COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

### **COURSE OBJECTIVES:**

- To gain knowledge on issues in designing RFIC and concepts of transistors.

- To gain knowledge on integrated circuits design using Passive components.

- To gain knowledge on RF Amplifiers and RF Mixers designs.

### **COURSE OUTCOMES:**

### Upon completion of this course, the students will have:

- CO1: Detailed Knowledge on issues in designing RFIC and concepts of transistors.

- CO2: Ability to design integrated circuits using Passive components.

- CO3: Detailed Knowledge on RF Amplifiers and RF Mixers designs.

### **TOPICS COVERED:**

### ISSUES IN RFIC DESIGN, NOISE, LINEARITY, AND FILTERING:

Lower frequency analog design and microwave design versus radio frequency integrated circuit design - Impedance levels for microwave and low-frequency analog design- noise - linearity and distortion in RF Circuits - dynamic range - filtering issue.

### REVIEW OF TECHNOLOGY

Small -signal model of bipolar transistor - high frequency effects - noise in bipolar transistors - base shot noise-noise sources in the transistor model - bipolar transistor design considerations-CMOS transistor.- impedance matching - tapped capacitors and inductors - the concept of mutual inductance - tuning a transformer - bandwidth of an impedance transformation network-quality factor of an LC resonator.

### DESIGN OF PASSIVE CIRCUIT ELEMENTS IN IC TECHNOLOGIES: (9)

Technology backend and metallization in IC technologies - sheet resistance and skin effect -parasitic capacitance and inductance -current handling in metal lines-design of inductors and transformers - characterization of inductor-layout of spiral inductors - on-chip transmission lines - high frequency measurements of on-chip passives and common De-Embedding techniques-packaging.

### LNA AND POWER AMPLIFIER: (9

Basic amplifiers - amplifiers with feedback - noise in amplifiers - linearity in amplifiers - differential pair and other differential amplifiers-low-voltage topologies for LNAs and the use of on-chip transformers - DC bias networks - temperature effects - broad band LNA design. Power amplifier: power capability - efficiency calculations - matching considerations - Class A,B,C.D.E.F,G,H and S amplifiers -summary of amplifier classes for RF Integrated circuits - AC load line - matching to achieve desired power -

packaging -effects and implications of non linearity - linearization techniques - CMOS power amplifier example.

MIXERS: (9)

Mixing with nonlinearity - basic mixer operation - controlled transconductance mixer - double-balancedmixer - mixer with switching of upper quad - analysis of switching modulator-mixer noise - linearity - improving isolation - image reject and single -sideband mixers-alternative mixer designs - general design comments-CMOS mixers.

LECTURE: 45 PERIODS TUTORIAL: 0 PERIODS PRACTICAL: 0 PERIODS TOTAL: 45 PERIODS

### Reference Books:

- 1. John Rogers and Calvin Plett, "Radio Frequency Integrated Circuit Design", Artech House, 2002.

- 2. Stephan A Mass, "Non-Linear Microwave and RF circuits", Artech House.

-8 9 -8 G

- 3. Ferri Losee, "RF Systems, Components and Circuits handbook", Artech house, 2002.

- 4. Larson LE, "RF and Microwave Circuit for Wireless Applications", Artech House, 1997.

|     | PO1 | PO2 | PO3 | PO4             | PO5 | PO6  | PO7 | PO8 | PO9 | PO10 | PO11 |

|-----|-----|-----|-----|-----------------|-----|------|-----|-----|-----|------|------|

| CO1 | 3   | -   | -   | -               | 1   | 1    | 1   | 1   | -   | =    | 1    |

| CO2 | 2   | 3   | -   | : <del></del> : | 1   | ile: | 商   | 1   | π   | -    | 1    |

| CO3 | 1   | -   | 1   | 1               | 1   | 1    | 25  | 1   | 1   | -    | 100  |

# 16VLPE04 MICROSENSORS AND MEMS (Common to Applied Electronics)

L T P C 3 0 0 3

## CORE/ELECTIVE COURSE: Elective

## **PREREQUISITES:**

Basic science, Basic engineering.

#### COURSE ASSESSMENT METHODS: Both continuous and semester-end assessment.

#### **COURSE OBJECTIVES:**

- To understand the microfabrication process, MEMS materials and various system issues.

- To acquire basic knowledge on electrical and mechanical concepts of MEMS.

- To acquire knowledge on various types of microsensors.

- To introduce the concepts of optical and RF MEMS and various case studies.

#### **COURSE OUTCOMES:**

#### Upon completion of this course, the students will have:

- CO 1: Knowledge on microfabrication process, MEMS materials and various system issues

- CO 2: Basic knowledge on electrical and mechanical concepts of MEMS.

- CO 3: Knowledge on various types of microsensors.

- CO 4: Introduction to optical and RF MEMS and various case studies.

#### TOPICS COVERED:

#### MICROFABRICATION AND MATERIALS

(9)